가. 기억장치의 용량

나. 기억장치의 위치

다. 기억장치의 액세스 속도

라. CPU의 직접 액세스 가능 여부

[보기] 직접 액세스, 임의 액세스, 연관 액세스, 순차적 액세스

__(가)__: 기억장치에 저장된 정보들을 처음부터 순서대로 액세스하는 방식.__(나)__: 읽기/쓰기 장치를 정보가 위치한 근처로 직접 이동시킨 다음에, 순차적 검색으로 최종 위치에 도달하여 액세스하는 방식.__(다)__: 기억장치 내의 모든 저장장소들이 고유의 주소를 가지고 있기때문에, 어떤 임의의 주소도 직접 선택하여 액세스하는 방식.__(라)__: 각 기억 장소에 포함된 키(key)값의 검색을 통하여 액세스 할 위치를 찾아내는 방식.

__(가)__은 주소와 읽기/쓰기 신호가 기억장치에 도착한 순간부터 데이터가 저장되거나 읽혀지는 동작이 왼료되는 순간까지의 시간을 말한다.__(나)__은__(가)__과 데이터 복원 시간을 합한 시간을 말한다.

📄 답지

가. 기억장치의 용량

나. 기억장치의 위치

다. 기억장치의 액세스 속도

라. CPU의 직접 액세스 가능 여부

정답 : 라.

기억장치는 CPU가 직접 액세스할 수 있는 내부 기억장치(internal memory)와 장치 제어기(device controller)를 통하여 액세스할 수 있는 외부 기억장치(external memory)로 구성된다.

[보기] 직접 액세스, 임의 액세스, 연관 액세스, 순차적 액세스

__(가)__: 기억장치에 저장된 정보들을 처음부터 순서대로 액세스하는 방식.__(나)__: 읽기/쓰기 장치를 정보가 위치한 근처로 직접 이동시킨 다음에, 순차적 검색으로 최종 위치에 도달하여 액세스하는 방식.__(다)__: 기억장치 내의 모든 저장장소들이 고유의 주소를 가지고 있기때문에, 어떤 임의의 주소도 직접 선택하여 액세스하는 방식.__(라)__: 각 기억 장소에 포함된 키(key)값의 검색을 통하여 액세스 할 위치를 찾아내는 방식.

정답

(가) : 순차적 액세스

(나) : 직접 액세스

(다) : 임의 액세스

(라) : 연관 액세스

__(가)__은 주소와 읽기/쓰기 신호가 기억장치에 도착한 순간부터 데이터가 저장되거나 읽혀지는 동작이 왼료되는 순간까지의 시간을 말한다.__(나)__은__(가)__과 데이터 복원 시간을 합한 시간을 말한다.

정답

(가) : 액세스 시간(access time)

(나) : 기억장치 사이클 시간(memory cycle time)

** 반도체 기억장치나 디스크와 같은 최근의 저장장치들은 읽기 동작 후에 정보가 지워지지 않기때문에 데이터 복원 시간이 없고, 액세스 시간과 기억장치 사이클 시간이 같다.

정답 : 160[MBytes/sec]

데이터 전송률은 기억장치로부터 초당 읽혀지거나 쓰여질 수 있는 비트수를 말하며 아래와 같이 구할수 있다.

데이터 전송률 = (1 / 액세스 시간) X (한 번에 읽혀지는 데이터 바이트의 수)

데이터 전송률 = {1 / (50 X 10-9)} X (64/8) = 160[MBytes/sec]

1번. 빈칸에 알맞은 답을 채워주세요

1) ________ 는 CPU와 주기억장치 간의 속도 차이를 보완해주기 위하여 데이터를 일시 저장해주는 중간 버퍼 기능을 수행한다.

계층적 기억 장치 시스템을 구성하면 하위 계층으로 내려갈수록 용량이 더 2) ________ 비트당 가격은 3) ________ 반면에 지역성의 원리로 인하여 액세스 빈도가 더 4) ________

진다.

2번. 다음 지문들의 참 거짓 여부를 표시하세요.

[ ] 기억장치를 계층적으로 구성함으로써 속도와 용량 및 가격 면에서 더 개선된 기억장치시스템을 구성할 수 있다.

[ ] 짧은 시간을 기준으로 보면 CPU가 기억장치의 한정된 몇몇 영역들을 주로 액세스하면서 작업을 수행하는데, 이와 같은 현상을 지역성의 원리라고 한다.

[ ] 기억장치 계층에서 상위 계층으로 올라갈수록 용량이 감소하고, 액세스 시간은 짧아지며, CPU에 의한 액세스 빈도는 낮아진다.

3번. 계층적 기억장치시스템에서 첫 번째 계층 기억장치의 액세스 시간이 20ns 이고 두 번째 계층 기억장치의 액셰스 시간은 200ns이다. 첫 번째 계층 기억장치의 적중률이 0.8이라먼,평균 기억장치 액세스 시간은 얼마인가?

📄 답지

1번. 빈칸에 알맞은 답을 채워주세요

1) 캐시 메모리 는 CPU와 주기억장치 간의 속도 차이를 보완해주기 위하여 데이터를 일시 저장해주는 중간 버퍼 기능을 수행한다.

계층적 기억 장치 시스템을 구성하면 하위 계층으로 내려갈수록 용량이 더 2) 커지고 비트당 가격은 3) 떨어지는 반면에 지역성의 원리로 인하여 액세스 빈도가 더 4) 낮아진다

진다.

2번. 다음 지문들의 참 거짓 여부를 표시하세요.

[ O ] 기억장치를 계층적으로 구성함으로써 속도와 용량 및 가격 면에서 더 개선된 기억장치시스템을 구성할 수 있다.

[ O ] 짧은 시간을 기준으로 보면 CPU가 기억장치의 한정된 몇몇 영역들을 주로 액세스하면서 작업을 수행하는데, 이와 같은 현상을 지역성의 원리라고 한다.

[ X ] 기억장치 계층에서 상위 계층으로 올라갈수록 용량이 감소하고, 액세스 시간은 짧아지며, CPU에 의한 액세스 빈도는 낮아진다.

: CPU에 의한 액세스 빈도는 높아진다.

3번. 계층적 기억장치시스템에서 첫 번째 계층 기억장치의 액세스 시간이 20ns 이고 두 번째 계층 기억장치의 액셰스 시간은 200ns이다. 첫 번째 계층 기억장치의 적중률이 0.8이라먼,평균 기억장치 액세스 시간은 얼마인가?

20 * 0.8 + 200 * 0.2 = 56ns

1번. 초기의 컴퓨터는 주기억장치로 임의 액세스 저장장치인 자기 코어(magnetic core)를 사용했으나, 최근 대부분의 컴퓨터는 주기억장치 소자로서 반도체 기억장치 칩들을 사용하고 있다. (O / X)

2번. 반도체 기억장치 중에서 RAM / ROM 은 읽기와 쓰기가 모두 가능하며, RAM / ROM 은 내용을 읽는 것만 가능하고 쓰는 것은 불가능하다.

3번. RAM은 제조 기술에 따라 DRAM과 SRAM으로 분류되는데, 이 중 DRAM / SRAM 은 캐패시터(capacitor)에 전하를 충전하는 방식으로 데이터를 저장하며, 이 때문에 주기적인 재충전(refresh)이 필요한 반도체 기억장치이다.

4번. DRAM은 비휘발성인 반면, SRAM은 휘발성이다. (O / X)

5번. DRAM은 주로 주기억장치 / 캐시 로 사용되며, SRAM은 주기억장치 / 캐시 로 사용된다.

6번. 다음 중 ROM 칩에 필요하지 않는 신호는? [기본문제 5.14]

(1) 칩 선택 신호 (2) 주소 (3) 읽기 신호 (4) 쓰기 신호

7번. 다음 중에서 전원 공급이 중단되어도 내용이 지워지지 않으며, 전기적으로 지우고 다시 쓸 수도 있는 반도체 기억장치는? [기본문제 5.16]

(1) ROM (2) EPROM (3) EEPROM (4) SRAM

📄 답지

1번. 초기의 컴퓨터는 주기억장치로 임의 액세스 저장장치인 자기 코어(magnetic core)를 사용했으나, 최근 대부분의 컴퓨터는 주기억장치 소자로서 반도체 기억장치 칩 들을 사용하고 있다. (O)

2번. 반도체 기억장치 중에서 RAM 은 읽기와 쓰기가 모두 가능하며, ROM 은 내용을 읽는 것만 가능하고 쓰는 것은 불가능하다.

3번. RAM은 제조 기술에 따라 DRAM과 SRAM으로 분류되는데, 이 중 DRAM 은 캐패시터(capacitor)에 전하를 충전하는 방식으로 데이터를 저장하며, 이 때문에 주기적인 재충전(refresh)이 필요한 반도체 기억장치이다.

SRAM은 플립-플롭(flip-flop) 기억 셀을 이용하며, 전력이 공급되는 동안에는 데이터가 계속 유지된다는 특징이 있다.

4번. DRAM은 비휘발성인 반면, SRAM은 휘발성이다. (X)

DRAM과 SRAM은 모두 휘발성 기억장치이다.

5번. DRAM은 주로 주기억장치 로 사용되며, SRAM은 캐시 로 사용된다.

DRAM은 SRAM보다 밀도가 높고, 같은 용량 대비 가격이 저렴하며, 주로 기억장치로 사용된다.

SRAM은 DRAM보다 속도가 빠르며, 주로 캐시로 사용된다.

6번. 다음 중 ROM 칩에 필요하지 않는 신호는? [기본문제 5.14]

(1) 칩 선택 신호 (2) 주소 (3) 읽기 신호 (4) 쓰기 신호

정답: (4) 쓰기 신호

ROM은 데이터를 쓰는 기능이 없으므로 쓰기 신호는 필요하지 않다.

7번. 다음 중에서 전원 공급이 중단되어도 내용이 지워지지 않으며, 전기적으로 지우고 다시 쓸 수도 있는 반도체 기억장치는? [기본문제 5.16]

(1) ROM (2) EPROM (3) EEPROM (4) SRAM

정답: (3) EEPROM

ROM: 저장된 내용을 읽는 것만 가능한 반도체 기억장치

EPROM(Erasable PROM): 자외선을 이용하여 저장된 내용을 삭제할 수 있어서 여러 번의 갱신이 가능한 PROM(Programmable ROM)

EEPROM(Electrically Erasable PROM): 비휘발성이면서도 읽기와 쓰기가 모두 가능하며, 전기적으로도 삭제할 수 있는 PROM

SRAM: 플립-플롭(flip-flop) 기억 셀을 이용하며, 전력이 공급되는 동안에는 데이터가 계속 유지되는 RAM

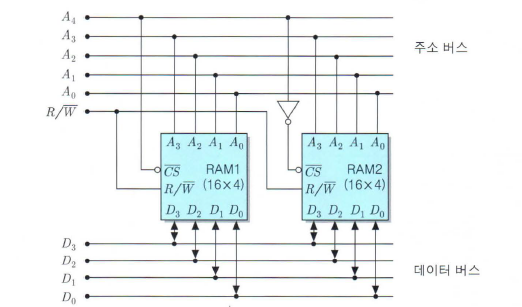

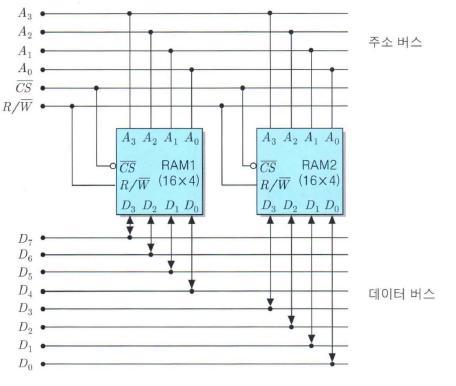

1번 다음은 n * m 크기의 메인메모리 모듈을 디자인한 그림입니다. 각 빈칸에 대해서 알맞게 채워주세요.

- 주소버스

_개, 데이터 입출력 비트가_개인_ * _bits크기의 RAM Chip들을직렬 / 병렬접속으로_ * _bits크기의 메인메모리를 디자인했다.

- 주소버스

_개, 데이터 입출력 비트가_개인_ * _bits크기의 RAM Chip들을직렬 / 병렬접속으로_ * _bits크기의 메인메모리를 디자인했다.

2번 [연습문제 5.4]

다음과 같은 조직을 가진 RAM들을 이용하여 1K * 32비트 기억장치 모듈을 구성하는데 필요한 칩의 수를 구하라

(1) 512 * 1비트 조직 :

(2) 128 * 4비트 조직 :

(3) 64 * 8비트 조직 :

📄 답지

1번

다음은 n * m 크기의 메인메모리 모듈을 디자인한 그림입니다.

각 빈칸에 대해서 알맞게 채워주세요.

주소버스 4개 데이터 입출력 비트가 4개인 16 * 4bit크기의 RAM Chip들을 [직렬] / 병렬접속으로 32 * 4bit 크기의 메인메모리를 디자인했다.

- 각 RAM은 4개의 비트로 기억장소의 위치를 결정한다.

- 한 램은 총 16개씩 0000 ~ 1111까지 가질 수 있지만 두 RAM을 직렬접속하면 최상단비트를 칩셀렉터로 사용해 1bit 증가된 효과를 얻을 수 있다.

- 상위비트를 0,1로 set하면 00000 ~ 01111, 10000 ~ 11111까지 선택할 수 있으므로, 총 32개의 주소를 선택해 데이터 입출력을 할 수 있다.

주소버스 4개, 데이터 입출력 비트가 4개인 16 * 4bits 크기의 RAM Chip들을 직렬 / [병렬]접속으로 16 * 8bits 크기의 메인메모리를 디자인했다.

- 컴퓨터 워드는 8bit인데 RAM크기가 4bit일때 두개의 RAM을 병렬접속하여 8비트 입출력크기를 만들 수 있다.

- 칩셀렉터를 공유하고, 주소버스 4비트에 있는 데이터를 2개의 칩이 받아서 데이터버스에 총 8비트씩 입, 출력시킬 수 있다.

2번 [연습문제 5.4]

다음과 같은 조직을 가진 RAM들을 이용하여 1K * 32비트 기억장치 모듈을 구성하는데 필요한 칩의 수를 구하라

-

1K * 32는 기억장소가 2^10, 데이터 입출력이 32비트를 가짐.

-

앞으로 곱 = 직렬 ,뒤로 곱 = 병렬

(1) 512 * 1비트 조직 : 2개의 직렬연결 2 * (512) => 1K * 1bits => 뒤로 32개 병렬연결 (1K * 1bits) * 32 => 1K * 32bits

(2) 128 * 4비트 조직 : 8개의 직렬연결 8 * (128), 8개의 병렬연결 (4) * 8

(3) 64 * 8비트 조직 : 16개의 직렬연결 16 * (64), 4개의 병렬연결 (8) * 4